### RANCANG BANGUN GENERATOR SET UJI UNTUK DIAGNOSIS KESALAHAN RANGKAIAN MULTIPLEXER QUAD 2 LINE TO 1 LINE IC 74157 MENGGUNAKAN METODE TABEL KESALAHAN BERBASIS ARDUINO NANO ATMEGA328

(Tesis)

# Oleh RIZKIMA AKBAR SETIAWAN

PROGRAM PASCASARJANA MAGISTER TEKNIK ELEKTRO

FAKULTAS TEKNIK

UNIVERSITAS LAMPUNG

BANDAR LAMPUNG

2023

### RANCANG BANGUN GENERATOR SET UJI UNTUK DIAGNOSIS KESALAHAN RANGKAIAN MULTIPLEXER QUAD 2 LINE TO 1 LINE IC 74157 MENGGUNAKAN METODE TABEL KESALAHAN BERBASIS ARDUINO NANO ATMEGA328

### Oleh RIZKIMA AKBAR SETIAWAN

**Tesis**

Sebagai Salah Satu Syarat untuk Mencapai Gelar MAGISTER TEKNIK ELEKTRO

Pada

Program Pascasarjana Magister Teknik Elektro Fakultas Teknik Universitas Lampung

PROGRAM PASCASARJANA MAGISTER TEKNIK ELEKTRO

FAKULTAS TEKNIK

UNIVERSITAS LAMPUNG

BANDAR LAMPUNG

2023

#### **ABSTRACT**

### DESIGN SET-TEST GENERATOR FOR FAULT DIAGNOSIS OF MULTIPLEXER QUAD 2 LINE TO 1 LINE IC 74157 USING FAULT TABLE METHOD ON ARDUINO NANO ATMEGA238-BASED

By

### RIZKIMA AKBAR SETIAWAN

A combinational digital circuit is composed of several logic gates whose output conditions are caused by the input conditions of the circuit. Minor faults in combinational digital circuits become a fundamental problem. These minor faults will cause temporary or permanent disturbances to the main output if they are not detected. This study aims to build a test generator set that successfully detects faults and locations in the quad 2-line to 1-line IC 74157 multiplexer circuit. The fault table method is used to compile a fault diagnosis tree as a test set embedded in a test generator set. The complete generator set test consists of 4 generator set test pieces of the multiplexer quad 2-lines to 1-line IC 74157. Each part of the circuit consists of 4 inputs with the Boolean equation  $Y = \overline{A}C\overline{D} + \overline{A}BD$  which consists of 11 lines. The test results on the IC 74157 quad 2-line to 1-line multiplexer circuit section provide an efficiency of 68.75% - 81.25%, with the most extended test being 5 levels. Complete testing of the entire quad 2-line to 1-line multiplexer IC 74157 gives an efficiency of 98.05% - 98.83%, with the most extended test being 20 levels.

**Keyword:** Fault, Multiplexer quad 2-line to 1-line IC 74157, Faults Table Method, Set-test Generator.

#### **ABSTRAK**

### RANCANG BANGUN GENERATOR SET UJI UNTUK DIAGNOSIS KESALAHAN RANGKAIAN MULTIPLEXER *QUAD 2 LINE TO 1 LINE* IC 74157 MENGGUNAKAN METODE TABEL KESALAHAN BERBASIS ARDUINO NANO ATMEGA238

Oleh

### RIZKIMA AKBAR SETIAWAN

Rangkaian digital kombinasional merupakan rangkaian yang tersusun dari beberapa gerbang logika dengan kondisi keluaran disebabkan oleh kondisi masukan rangkaian tersebut. Kesalahan kecil pada rangkaian digital kombinasional menjadi masalah penting. Jika kesalahan kecil tersebut tidak terdeteksi maka akan menyebabkan gangguan sementara bahkan permanen pada keluaran utamanya. Peneltian ini bertujuan untuk membangun generator set uji yang berhasil mendeteksi kesalahan dan lokasi kesalahan pada rangkaian *multiplexer quad 2 line* to 1 line IC 74157. Metode tabel kesalahan digunakan untuk menyusun pohon diagnosa kesalahan sebagai set pengujian yang ditanamkan pada generator set uji. Generator set uji lengkap tediri dari 4 buah generator set uji potongan rangkaian multiplexer quad 2 line to 1 line IC 74157. Setiap potongan rangkaian terdiri dari 4 *input* dengan persamaan Boolean  $Y = \overline{A}C\overline{D} + \overline{A}BD$  yang terdiri dari 11 jalur. Hasil pengujian pada potongan rangkaian multiplexer quad 2 line to 1 line IC 74157 memberikan efisiensi sebesar 68,75% - 81,25% dengan pengujian terpanjang adalah 5 level. Pengujian lengkap keseluruhan rangkaian multiplexer quad 2 line to 1 line IC 74157 memberikan efisiensi sebesar 98,05% - 98,83% dengan pengujian terpanjang adalah 20 level.

**Kata Kunci:** Kesalahan, *Multiplexer quad* 2 *line to* 1 *line* IC 74157, Metode Tabel Kesalahan, Generator Set Uji.

: RANCANG BANGUN GENERATOR SET UJI UNTUK DIAGNOSIS KESALAHAN RANGKAIAN **MULTIPLEXER QUAD 2 LINE TO 1 LINE IC** 74157 MENGGUNAKAN METODE TABEL **KESALAHAN BERBASIS ARDUINO NANO**

: Rizkima Akbar Setiawan

Nomor Pokok Mahasiswa

: 2025031010

Program Studi

: Magister Teknik Elektro

**Fakultas**

: Teknik

MENYETUJUI

1. Komisi Pembimbing

Pembimbing II

Dr. Eng. Ageng Sadnowo R., S.T., M.T. Dr. Eng. F.X. Arinto S., S.T., M.T.

NIP 19690228 199803 1 001

NIP 19691219 199903 1 002

2. Ketua Program Studi Magister Teknik Elektro

Misfa Susanto, S.T., M.T., Ph.D. NIP 19710525 199903 1 001

1. Komisi Penguji

Ketua Komisi Penguji (Pembimbing I) AMPUNG UNIVERSITAS LAM

: Dr. Eng. Ageng S. R., S.T., M.T.

Sekretaris Komisi Penguji AVERSITAS LAMPUNG UNIVERSI (Pembimbing II)

APUNG UNIVERSITAS LAMPUN

(Pembimbing II) : Dr. Eng. F.X. Arinto S., S.T., M.T.

Anggota Komisi Penguji

(Penguji I) UNG UNIVERS : Dr. Ir. Sri Ratna Sulistiyanti, M.T.

Anggota Komisi Penguji

(Penguji II)

: Dr. Sri Purwiyanti, S.T., M.T.

2. Dekan Fakultas Teknik

Dr. Eng. Ir. Helmy Fitriawan, S.T., M.Sc.

NIP 19750928 200112 1 002

r. Murhadi, M.Si.

0326 198902 1 001

Tanggal Lulus Ujian Tesis: 22 Juni 2023

#### **SURAT PERNYATAAN**

Dengan ini Saya menyatakan bahwa sesungguhnya tesis yang saya susun sebagai syarat untuk mendapatkan gelar Magister Teknik pada Progam Pascasarjana Magister Teknik Elektro seluruhnya adalah benar merupakan hasil karya sendiri.

Adapun bagian-bagian tertentu dalam penulisan tesis ini, saya kutip dari hasil penulisan orang lain yang sumbernya dituliskan dengan jelas sesuai dengan norma, kaidah dan etika penulisan karya ilmiah.

Tesis dengan judul "Rancang Bangun Generator Set Uji untuk Diagnosis Kesalahan Rangkaian *Multiplexer Quad 2 Line to 1 Line* IC 74157 Menggunakan Metode Tabel Kesalahan Berbasis Arduino Nano Atmega328" dapat diselesaikan berkat bimbingan dan motivasi dari pembimbing-pembimbing saya, yaitu:

- 1. Dr. Eng. Ageng Sadnowo Repelianto, S.T., M.T.

- 2. Dr. Eng. F.X. Arinto Setyawan, S.T., M.T.

Saya ucapkan terima kasih yang sebesar-besarnya kepada semua pihak, khususnya kedua dosen pembimbing dan Bapak/ Ibu Dosen Progam Studi Magister Teknik Elektro Universitas Lampung yang telah banyak memberikan ilmu pengetahuan, bimbingan dan motivasi.

Apabila dikemudian hari ditemukan seluruh atau sebagian tesis yang saya buat ini bukan hasil karya saya sendiri atau adanya plagiat dalam bagian-bagian tertentu, saya bersedia menerima sanksi akademik sesuai dengan peraturan perundangan yang berlaku.

Bandar Lampung, 26 Juni 2023

Rizkima Akbar Setiawan NPM: 2025031010

#### **RIWAYAT HIDUP**

Penulis dilahirkan di Pringsewu, Lampung, pada tanggal 15 Maret 1997. Penulis merupakan anak tunggal, dari pasangan Bapak Bambang Hariyanto, S.H dan Ibu Fatimah S.E.

Penulis pertama kali mengenyam pendidikan di TK Aisyah Ambarawa. Penulis melanjutkan tingkat sekolah dasar di SD Negeri 1 Margodadi Kec. Ambarawa lulus tahun 2009. Sekolah Menengah Pertama diselesaikan di SMP Negeri 1 Pringsewu Kec.

Pringsewu, lulus tahun 2012. Sekolah Menengah Atas diselesaikan di SMA Negeri 1 Gadingrejo Kec. Gadingrejo, lulus tahun 2015. Penulis melanjutkan pendidikan ke jenjang perguruan tinggi di Universitas Lampung pada Jurusan Teknik Elektro tahun 2015 melalui jalur Mandiri (UM).

Selama menimba ilmu di Universitas Lampung penulis aktif dalam orgnisasi Badan Mahasiswa Pringsewu Seluruh Indonesia (BMP-SI) menyandang jabatan sebagai Menteri Pemberdayaan Lingkungan pada tahun 2017.

Pada Tahun 2018, Penulis melaksanakan Kerja Praktik (KP) di PTPN VII Unit Usaha Way Berulu Pesawaran selama satu bulan. Penulis menyelesaikan Kerja Praktik dengan menulis sebuah laporan yang berjudul: "Sistem *Control* Suhu Ruang Menggunakan *Resistance Temperature Detector PT100 3Wire* pada *Oven* Pengasapan Karet RSS (*Ribbed Smoked Sheets*) di PT. Perkebunan Nusantara VII Unit Usaha Way Berulu".

Pada Tahun 2019, Penulis menyelesaikan program studi S1 Teknik Elektro dengan menulis sebuah skripsi yang berjudul: "Perancangan Setrika Listrik Tanpa Kabel dengan Pengaturan Suhu Otomatis Berbasis Arduino Uno".

Pada Tahun 2020 penulis terdaftar sebagai Mahasiswa Program Pascasarjana Teknik Elektro Universitas Lampung melalui jalur Beasiswa bebas SPP. Dan pada tahun 2022 penulis melakukan penelitian pada bidang mikrokontroler dengan judul tesis "Rancang Bangun Generator Set Uji untuk Diagnosis Kesalahan Rangkaian *Multiplexer Quad 2 Line to 1 Line* IC 74157 Menggunakan Metode Tabel Kesalahan Berbasis Arduino Nano Atmega328" dibawah bimbingan Bapak Dr. Eng. Ageng Sadnowo Repelianto, S.T., M.T. dan Bapak Dr. Eng. F.X. Arinto Setyawan, S.T., M.T.

Bandar Lampung, 26 Juni 2023 Penulis

RIZKIMA AKBAR SETIAWAN

### **PERSEMBAHAN**

Dengan Ridho Allah SWT, teriring shalawat kepada Nabi Muhammad SAW

Karya Tulis ini kupersembahkan untuk:

### Ayah dan Ibuku Tercinta

Bambang Hariyanto, S.H. dan Fatimah, S.E.

### **Keluarga Tersayang**

Keluarga Besar H. S. Markam dan Keluarga Besar Pangeran Usman serta Keluarga besarku di Masa Depan

### **Dosen Teknik Elektro**

Yang selalu membimbing, mengajarkan, memberikan saran, baik secara akademis maupun non akademis

### Teman- teman kebanggaanku

Rekan – rekan Jurusan Teknik Elektro

### Sahabat-sahabatku

Yang selalu membantu, memberikan semangat, mendukung menuju keberhasilan, serta berbagi cerita suka duka dalam berkeluh kesah

### Keluarga Besar Magister Teknik Elektro 2020

Yang selalu memberi semangat, dukungan dalam proses yang sangat panjang, dan selalu berdiri bersama dalam perjuangan menuju kesuksesan

### Almamaterku

Universitas Lampung

### Bangsa dan Negaraku

Republik Indonesia

Terima kasih untuk semua yang telah diberikan kepadaku. Jazzakallah Khairan.

### **MOTTO**

"Jangan Pernah Berhenti Berbuat Baik untuk Orang Lain Walaupun Orang Itu akan Menyakitimu, Percayalah Hal Baik akan Selalu Datang Kepadamu"

"Pantang Menyerah Sebelum Dicoba, Pantang Pulang Sebelum Sukses dan Do'a Ibu adalah Segalanya"

— Rizkima Akbar Setiawan alias Akbar Tunggal

#### SAN WACANA

#### Assalamu'alaikum Wr. Wb.

Syukur Alhamdulillahirobbilalamin, Penulis haturkan puji syukur atas kehadirat Allah SWT yang senantiasa melimpahkan rahmat dan hidayah, serta inayah-Nya kepada penulis sehingga penulis dapat menyelesaikan laporan Tesis dengan mempersembahkan judul tesis "Rancang Bangun Generator Set Uji untuk Diagnosis Kesalahan Rangkaian *Multiplexer Quad 2 Line to 1 Line* IC 74157 Menggunakan Metode Tabel Kesalahan Berbasis Arduino Nano Atmega328" dengan sebaik-baiknya.

Shalawat beriring salam selalu tercurah kepada junjungan seluruh alam Nabi Muhammad SAW, sahabatnya, serta para pengikutnya yang selalu istiqomah diatas jalan agama islam hingga hari ajal menjemput.

Dalam penyusunan tugas akhir ini penulis banyak mendapat bimbingan, motivasi dan bantuan baik moral maupun materi oleh banyak pihak. Untuk itu dengan sepenuh ketulusan hati penulis mengucapkan terima kasih kepada:

- 1. Ibu Prof. Dr. Ir. Lusmeilia Afriani, D.E.A., I.P.M., selaku Rektor Universitas Lampung.

- 2. Bapak Prof. Dr. Ir. Murhadi, M.Si., selaku Direktur Program Pascasarjana Fakultas Teknik Universitas Lampung.

- 3. Bapak Dr. Eng. Helmy Fitriawan, S.T., M,Sc., selaku Dekan Fakultas Teknik, Universitas Lampung.

- 4. Ibu Herlinawati, S.T., M.T., selaku Ketua Jurusan Teknik Elektro Universitas Lampung.

- 5. Bapak Misfa Susanto, S.T., M.T., Ph.D. selaku Ketua Program Studi Magister Teknik Elektro Universitas Lampung.

- 6. Bapak Dr. Eng. Ageng Sadnowo Repelianto, S.T., M.T., selaku dosen pembimbing utama tesis sekaligus dosen pembimbing akademik yang banyak memberikan waktu, ide pemikiran dan semangat serta motivasi bagi penulis.

- 7. Bapak Dr. Eng. F.X. Arinto Setyawan, S.T., M.T., selaku pembimbing kedua tesis, yang telah banyak memberikan waktu, pengalaman, motivasi dan pemikiran bagi penulis.

- 8. Ibu Dr. Ir. Sri Ratna Sulistiyanti, S.T., M.T., selaku dosen penguji utama sekaligus yang telah banyak memberikan kritik, saran dan motivasi yang bermanfaat bagi penulis.

- 9. Ibu Dr. Sri Purwiyanti, S.T., M.T., Ph.D., selaku dosen penguji kedua yang telah banyak memberikan kritik dan saran yang bermanfaat bagi penulis.

- 10. Seluruh Dosen Program Studi Magister Teknik Elektro Universitas Lampung, berkat ilmu yang telah diajarkan kepada penulis selama penulis menjalani masa studi di perkuliahan.

- 11. Seluruh Tenaga Pendidik Program Studi Magister Teknik Elektro Fakultas Teknik Universitas Lampung yang telah banyak membantu kepada penulis, sehingga dapat menyelesaikan tugas akhir ini.

- 12. Seluruh teman-teman Program Studi Magister Teknik Elektro Unila angkatan 2020 untuk kebersamaan yang telah dijalani. Tiada kata yang dapat penulis utarakan untuk mengungkapkan perasaan senang dan bangga menjadi bagian dari angkatan 2020.

- 13. Serta semua pihak yang telah membantu dalam penyusunan tugas akhir ini yang tidak bisa penulis sebutkan satu-persatu.

- 14. Teman-teman sehidup semati di Teknik Elektro UNILA Kevin, Misbach, Bayu, Hendry, Fajar, Arsy, Catur, Iqbal, Kak Yudi, Mba Vivi, dan Tiya yang telah memberikan semangat juang, serta suasana yang sangat nyaman dalam menempuh gelar M.T.

Akhir kata, Penulis menyadari bahwa Tesis ini masih jauh dari kesempurnaan, baik dari segi isi maupun cara penyajiannya. Oleh karena itu, Penulis sangat mengharapkan saran serta kritik yang bersifat membangun dari pembaca. Akhir kata sedikit harapan penulis semoga karya sederhana ini dapat berguna dan bermanfaat bagi kita semua. Aamiin Allahumma Aamiin.

Wassalamu'alaikum Wr. Wb.

Bandar Lampung, 26 Juni 2023 Penulis,

Rizkima Akbar Setiawan

### **DAFTAR ISI**

|                            | Halaman |

|----------------------------|---------|

| HALAMAN JUDUL              | i       |

| ABSTRACT                   | iii     |

| ABSTRAK                    | iv      |

| LEMBAR PENGESAHAN          | v       |

| SURAT PERNYATAAN           | vii     |

| RIWAYAT HIDUP              | viii    |

| SAN WACANA                 | xii     |

| DAFTAR ISI                 | XV      |

| DA.FTAR TABEL              | xviii   |

| DAFTAR GAMBAR              | xix     |

| I. PENDAHULUAN             |         |

| 1.1. Latar Belakang        | 1       |

| 1.2. Rumusan Masalahan     | 3       |

| 1.3. Tujuan Penelitian     | 3       |

| 1.4. Manfaat Penelitian    | 3       |

| 1.5. Batasan Masalah       | 4       |

| 1.6. Hipotesis             | 4       |

| 1.7. Sistematika Penulisan | 4       |

| II. TINJAUAN PUSTAKA       | 6       |

| 2.1 Penelitian Terdahulu   | 6       |

| 2.2.   | Gangguan Digital                              |

|--------|-----------------------------------------------|

| 2.3.   | Karakteristik Gangguan                        |

| 2.4.   | Gerbang Logika                                |

| 2.4.   | Rangkaian Kombinasional                       |

| 2.6.   | Diagnosa Kesalahan                            |

| 2.7.   | Model Gangguan <i>Stuck</i> Logika            |

| 2.8.   | Pohon Diagnosa                                |

|        |                                               |

| III. M | ETODE PENELITIAN                              |

| 3.1.   | Waktu dan Tempat penelitian                   |

| 3.2.   | Alat dan Bahan Penelitian                     |

| 3.3.   | Prosedur Penelitian                           |

| 3.4.   | Metode yang Diusulkan                         |

| 3.5.   | Susunan Rangkaian Pengujian                   |

| 3.6.   | Metode Tabel Kesalahan                        |

|        | 3.6.1 Penyusunan Tabel Kesalahan              |

|        | 3.6.2 Penentuan Set Pengujian Lengkap Minimum |

|        | 3.6.3 Pohon Diagnosa                          |

| 3.7.   | Generator Set Uji                             |

|        | 3.7.1 Perancangan Pengujian                   |

|        | 3.7.2 Prosedur Generator Set Uji              |

| IV. H  | ASIL DAN PEMBAHASAN64                         |

|        | Hasil Penelitian                              |

| 7.1.   | 4.1.1 Hasil Generator Set Uji Pertama 64      |

|        |                                               |

|        | 4.1.2 Hasil Generator Set Uji Kedua           |

|        | 4.1.3 Hasil Generator Set Uji Ketiga          |

|        | 4.1.4 Hasil Generator Set Uji Keempat   | 68 |

|--------|-----------------------------------------|----|

|        | 4.1.5 Hasil Pengujian Generator Set Uji | 68 |

| 4.2.   | . Pembahasan                            | 69 |

| V. SII | MPULAN DAN SARAN                        | 87 |

|        | . Simpulan                              |    |

| 5.2.   | . Saran                                 | 87 |

| DAFT   | TAR PUSTAKA                             | 88 |

## **DAFTAR TABEL**

| Tabel |      | Halaman                                                          |

|-------|------|------------------------------------------------------------------|

|       | 2.1. | Keluaran Gerbang AND saat Normal dan Dalam Kondisi Stuck15       |

|       | 2.2. | Lokasi Kesalahan Gerbang AND Saat Normal dan Dalam Kondisi       |

|       |      | Stuck                                                            |

|       | 2.3. | Pemilihan Set Pengujian Lengkap                                  |

|       | 3.1. | Tabel Kebenaran IC 7415725                                       |

|       | 3.2. | Tabel Kesalahan Diagnosa Kesalahan Tunggal Rangkaian 126         |

|       | 3.3. | Kelompok Kesalahan Potongan Rangkaian Uji Pertama27              |

|       | 3.4. | Tabel Kesalahan Diagnosa Kesalahan Tunggal Rangkaian 228         |

|       | 3.5. | Kelompok Kesalahan Potongan Rangkaian Uji 229                    |

|       | 3.6. | Tabel Kesalahan Diagnosa Kesalahan Tunggal Rangkaian 330         |

|       | 3.7. | Kelompok Kesalahan Potongan Rangkaian Uji 331                    |

|       | 3.8. | Tabel Kesalahan Diagnosa Kesalahan Tunggal Rangkaian 432         |

|       | 3.9. | Kelompok Kesalahan Potongan Rangkaian Uji 433                    |

|       | 3.10 | ). Penentuan Set Pengujian Lengkap Minimum35                     |

|       | 4.1. | Hasil Pengujian Rangkaian Generator Set Uji Potongan 1 Rangkaian |

|       |      | Multiplexer IC 7415770                                           |

|       | 4.2. | Hasil Pengujian Rangkaian Generator Set Uji Potongan 2 Rangkaian |

|       |      | Multiplexer IC 7415774                                           |

|       | 4.3. | Hasil Pengujian Rangkaian Generator Set Uji Potongan 3 Rangkaian |

|       |      | Multiplexer IC 74157                                             |

|       | 4.4. | Hasil Pengujian Rangkaian Generator Set Uji Potongan 4 Rangkaian |

|       |      | Multiplexer IC 7415782                                           |

## **DAFTAR GAMBAR**

| Gambai | r                                                                                             | Halaman       |

|--------|-----------------------------------------------------------------------------------------------|---------------|

|        | 2.1. Ikatan antara Gangguan, Kesalahan , dan Kegagalan                                        | 1             |

|        | 2.2. Karakteristik Gangguan                                                                   | 1             |

|        | 2.3. Rangkaian Digital Kombinasional                                                          | 14            |

|        | 2.4. Konsep dasar Model Gangguan Stuck Logika                                                 | 14            |

| :      | 2.5. Pohon Diagnosa                                                                           | 18            |

| :      | 3.1. Diagram Alir Perancangan Generator Set Uji                                               | 21            |

| :      | 3.2. Diagram Tulang Ikan Tahapan Penelitian                                                   | 22            |

| :      | 3.3. Rangkaian Multiplexer Quad 2 Line to 1 Line IC 74157                                     | 23            |

| :      | 3.4. Penyederhanaan Rangkaian untuk Penurunan Pengujian                                       | 24            |

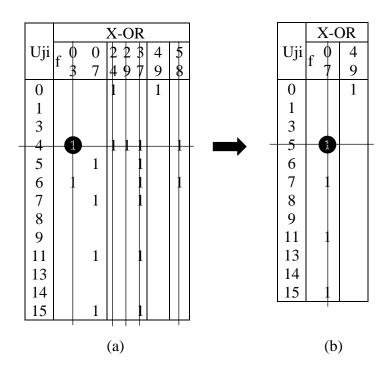

|        | 3.5. Menghilangkan Baris                                                                      | 34            |

| :      | 3.6. Menghilangkan Baris dan Kolom                                                            | 34            |

| :      | 3.7. Proses Penentuan Pengujian Penting Primer                                                | 37            |

| :      | 3.8. Penentuan Pengujian Penting Sekunder (10)                                                | 38            |

| :      | 3.9. Penentuan Pengujian Penting Sekunder (12)                                                | 39            |

| :      | 3.10. Penentuan Pengujian Penting Sekunder (4 dan 5)                                          | 39            |

| :      | 3.11. Penentuan Pengujian Tidak Penting (0)                                                   | 40            |

| :      | 3.12. Pemilihan Pengujian F*                                                                  | 41            |

| :      | 3.13. (a) Urutan $F^*_{00}(2,10)$ , (b) Urutan $F^*_{01}(2,10)$ , (c) Urutan $F^*_{10}(2,10)$ | $_{10}(2,0),$ |

|        | (d) Urutan $F^*_{11}(2,0)$ dengan 2 Level Pengujian                                           | 42            |

| :      | 3.14. Urutan Pohon Diagnosa dengan 3 Level Pengujian                                          | 43            |

| :      | 3.15. Urutan Pohon Diagnosa dengan 4 Level Pengujian                                          | 43            |

|        | 3.16. Urutan Pohon Diagnosa dengan 5 Level Pengujian                                          | 44            |

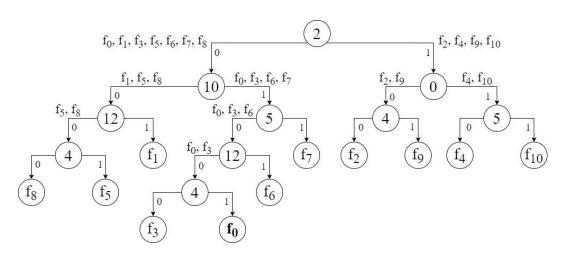

|        | 3.17. Pohon Diagnosa Potongan 1 Rangkaian IC 74157                                            | 44            |

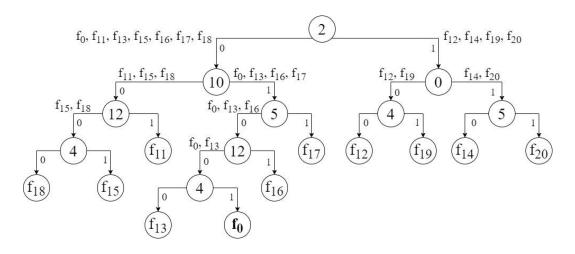

|        | 3.18. Pohon Diagnosa Potongan 2 Rangkaian IC 74157                                            | 45            |

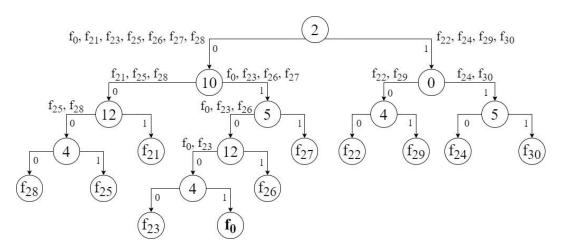

| 3.19. Pohon Diagnosa Potongan 3 Rangkaian IC 74157                      | 45   |

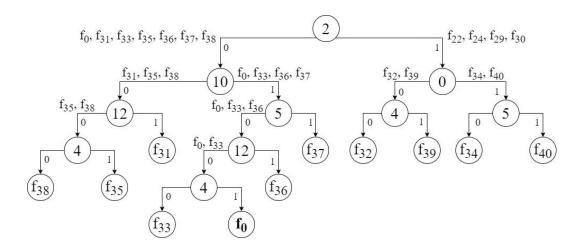

|-------------------------------------------------------------------------|------|

| 3.20. Pohon Diagnosa Potongan 4 Rangkaian IC 74157                      | 46   |

| 3.21. Pengaturan Eksperimen Rangkaian Set Uji                           | 47   |

| 3.22. Komponen Sistem Perangkat Lunak                                   | 47   |

| 3.23. Implementasi Potongan Rangkaian Uji Multiplexer                   | 48   |

| 3.24. Generator Set Uji                                                 | 49   |

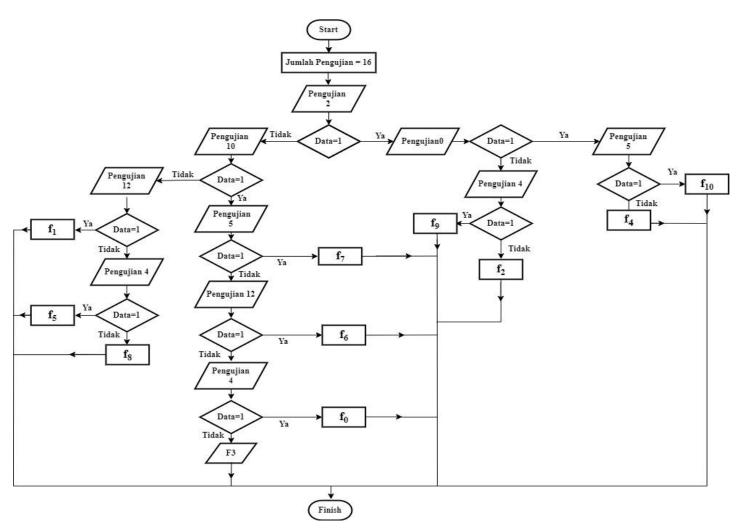

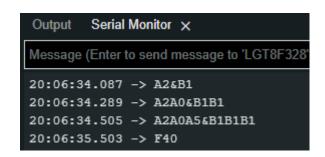

| 3.25. Hasil Serial Monitor Arduino IDE Rangkaian 1 IC 74157             | 51   |

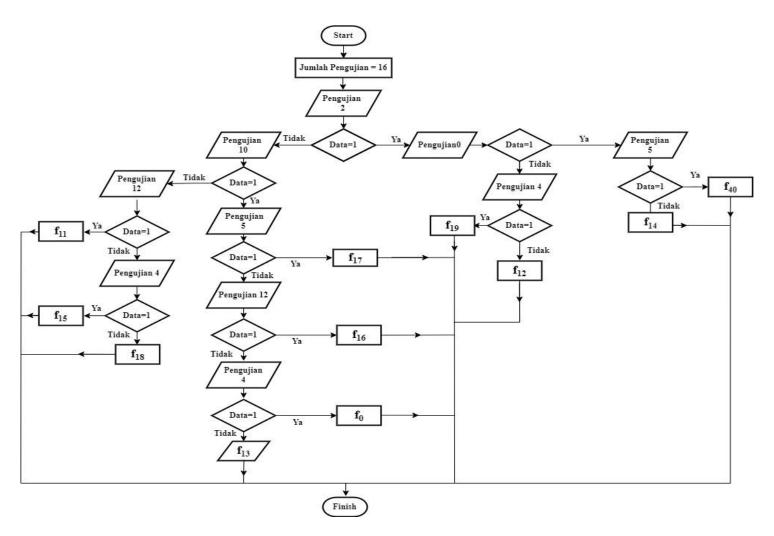

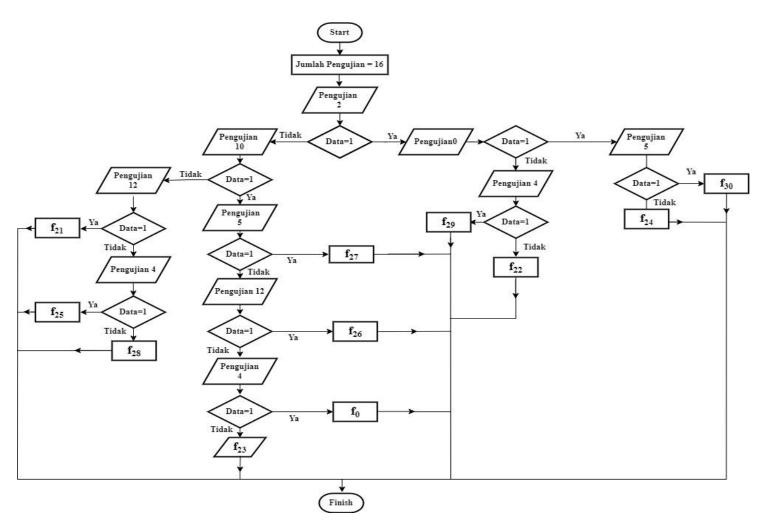

| 3.26. Diagram Alir <i>Coding</i> Arduino Nano Sebagai Generator Set Uji |      |

| Potongan 1 Rangkaian IC 74157                                           | . 52 |

| 3.27. Hasil Serial Monitor Arduino IDE Rangkaian 2 IC 74157             | 53   |

| 3.28. Diagram Alir <i>Coding</i> Arduino Nano Sebagai Generator Set Uji |      |

| Potongan 2 Rangkaian IC 74157                                           | 54   |

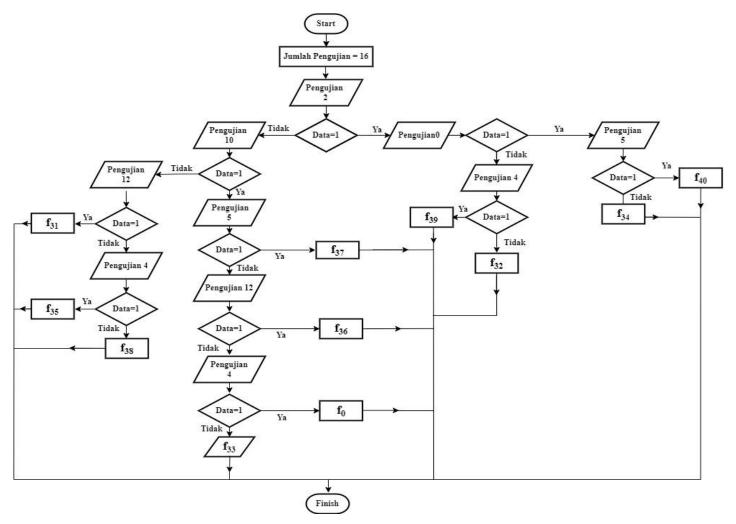

| 3.29. Hasil Serial Monitor Arduino IDE Rangkaian 3 IC 74157             | 55   |

| 3.30. Diagram Alir <i>Coding</i> Arduino Nano Sebagai Generator Set Uji |      |

| Potongan 3 Rangkaian IC 74157                                           | 56   |

| 3.31. Hasil Serial Monitor Arduino IDE Rangkaian 4 IC 74157             | 57   |

| 3.32. Diagram Alir <i>Coding</i> Arduino Nano Sebagai Generator Set Uji |      |

| Potongan 4 Rangkaian IC 74157                                           | 58   |

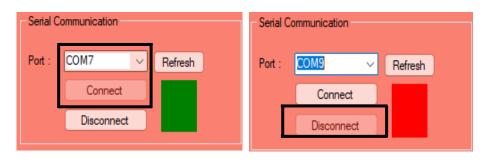

| 3.33. Serial Communication                                              | 60   |

| 3.34. Tampilan <i>Grid View</i>                                         | 61   |

| 3.35. Tampilan Text Box Description                                     | 62   |

| 4.1. GUI Generator Set Uji Pertama                                      | 65   |

| 4.2. GUI Generator Set Uji Potongan 2 Rangkaian IC 74157                | 66   |

| 4.3. GUI Generator Set Uji Potongan 3 Rangkaian IC 74157                | 67   |

| 4.4. GUI Generator Set Uji Potongan 4 Rangkaian IC 74157                | 68   |

| 4.5. Grafik Persentase Efesiensi Generator Set Uji 1                    | 71   |

| 4.6. Grafik Persentase Efesiensi Generator Set Uji 2                    | 75   |

| 4.7. Grafik Persentase Efesiensi Generator Set Uji 3                    | 79   |

| 4.8. Grafik Persentase Efesiensi Generator Set Uji 4                    | 83   |

#### I. PENDAHULUAN

### 1.1 Latar Belakang

Rangkaian digital kombinasional merupakan rangkaian dengan keadaan keluaranya disebabkan kondisi masukan rangkaian kombinasional tersebut [1]. Rangkaian digital kombinasional tersusun dari beberapa gerbang logika. Rangkaian kombinasional digital yang telah dirancang semestinya bekerja dengan baik sesuai yang diharapkan tanpa terjadi kendala.

Gangguan kecil telah menjadi masalah penting saat ini. Kesalahan yang sering terjadi dapat menyebabkan rangkaian digital kombinasional beroperasi secara tidak baik [2]. Kesalahan biasanya disebabkan oleh gangguan internal dalam jaringan rangkaian tersebut. Jika kesalahan kecil tersebut tidak terdeteksi maka akan menyebabkan gangguan sementara bahkan permanen pada keluaran utamanya [3].

Saat ini gangguan pada rangkaian digital menjadi perhatian utama dilingkup sistem digital *modern*. Dibutuhkan metode baru untuk mengatasi masalah yang ditimbulkan dari kesalahan tersebut yaitu dengan cara mendeteksi tiap kesalahan pada jalur rangkaian digital kombinasional dengan langkah dan waktu seminimal mungkin [4]. Jika terdeteksi kesalahan pada logika kombinasional akan menghasilkan dampak besar pada sistem operasi rangkaian yang harus diatasi dengan metode perbaikan yang tepat. Jenis gangguan yang sering terjadi adalah penyamaran logis yang membatasi propagasi dari letak kesalahan ke keluaran utama. Gangguan tersebut karena *input* gerbang lainya di sepanjang jalur propagasi menghentikan transisi arus menuju gerbang *output* [3].

Diagnosis merupakan pendeteksian untuk mencari kesalahan dan letak pasti dari kesalahan yang terjadi pada rangkaian digital. Salah satu cara untuk mendeteksi kesalahan dengan menggunakan generator dengan sistem dan rangkaian digital yang realistis sehingga hasil yang ditemukan akurat dan cepat [5]. Generator jenis ini tersusun dari beberapa gerbang logika dan rangkaian digital. Rangkaian digital yang terdiri dari rangkaian logika kombinasional dengan beberapa rangkaian IC secara signifikan, berbeda dengan rangkaian digital regular yang hanya berisi logika saja [6]. Koneksi antara gerbang logika pada rangkaian IC akan berproses jika telah terdeteksi kesalahan di jalur masukannya. Penyimpangan pada pola keluaranya dapat dikelompokan dalam himpunan kesalahan minimum [4].

Multi rangkaian terdiri dari beberapa sub-rangkaian kecil yang diekstraksi dan disintesis ulang menggunakan gerbang logika dua tingkat atau lebih yang ditujukan untuk meningkatkan keunggulanya [5]. Setiap sub-rangkaian yang telah diektraksi dengan proses percepatan yang telah diterapkan guna menghasilkan sub-rangkaian multilevel. Aplikasi ini akan mengurangi area sub-rangkaian yang disintesis ulang tanpa berdampak negatif pada rangkaian logika tersebut. Teknik ini mengambil keuntungan dari varians probabilitas pola masukan dari sub- rangkaian yang telah diekstraksi, sehingga akan meningkatkan fleksibelitas dalam mendeteksi kesalahan pada rangkaian digital karena mempersingkat jalur rangkaian digital yang dapat dipertimbangkan untuk mendeteksi kemungkinan terjadinya kesalahan pada pola masukan rangkaian digital kombinasional [5].

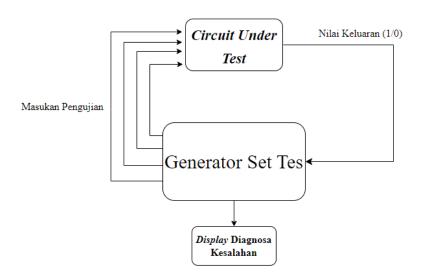

Berdasarkan uraian tersebut, maka diciptakan sebuah rancangan generator set uji untuk diagnosis gangguan di rangkaian digital kombinasional. Selain itu generator set uji dibuat untuk mengikuti perkembangan teknologi elektronika yang berkembang pesat. Sehingga dapat memudahkan pendeteksian gangguan pada perangkat elektronika secara otomatis. Pada penelitian ini generator set uji dibangun sesuai dengan pohon diagnosa yang dihasilkan dari metode tabel kesalahan. Generator set uji mendiagnosis kesalahan pada rangkaian digital kombinasional dengan Arduino nano sebagai pengontrol utamanya. Generator

set tes memodelkan kesalahan yang menghasilkan perubahan nilai jalur rangkaian dari 0 ke 1, atau 1 ke 0. Masing-masing pengujian menggunakan kesalahan *stuck at* 1 dan *stuck at* 0. Pengujian pada area rangkaian digital terjadi selama proses diagnosa kesalahan pada jalur masukan rangkaian digital kombinasional [7].

#### 1.2 Rumusan Masalah

Mengacu pada permasalahan yang ada maka rumusan perancangan ini adalah sebagai berikut:

- 1. Bagaimana menentukan set pengujian minimal untuk diagnosis kesalahan pada suatu rangkaian digital kombinasional menggunakan metode tabel kesalahan?

- 2. Bagaimana cara membangun generator set tes untuk uji rangkaian digital kombinasional?

### 1.3 Tujuan Penelitian

Adapun tujuan yang ingin dicapai pada penelitian ini adalah sebagai berikut:

- Membangun generator set uji untuk diagnosa gangguan pada rangkain multiplexer quad 2-line to 1-line IC 74157 menggunakan metode tabel kesalahan.

- Menganalisa efisiensi pengujian berdasarkan pohon diagnosa yang didapatkan dari metode tabel kesalahan

### 1.4 Manfaat Penelitian

Melalui penelitian ini, manfaat yang dapat diperoleh dari sistem yang dibangun adalah kesalahan rangkaian digital, sehingga para perancang dapat mengetahui terjadinya gangguan lebih awal pada sistem digital kombinasional yang diciptakan. Sehingga dapat tercapai standar reabilitasnya dan dihasilkan produk sesuai dengan yang diharapkan dengan kualitas yang bagus.

### 1.5 Batasan Masalah

Adapun pembatasan masalah dalam penelitian ini adalah seperti yang di bawah ini:

- 1. Pendeteksian gangguan hanya pada kesalahan tunggal yang bersifat tetap atau permanen pada rangkaian digital kombinasional.

- 2. Objek pengujian menggunakan *multiplexer quad 2-line to 1-line* IC 74157 IC 74157.

- 3. Generator set uji dibangun menggunakan Arduino nano atmega 328.

### 1.6 Hipotesis

Metode tabel kesalahan menghasilkan set pengujian lengkap minimum yang dipetakan menjadi sebuah pohon diagnosa. Implementasi dari pohon diagnosa yaitu perancangan generator set uji yang berhasil mendeteksi kesalahan dan lokasi terjadinya kesalahan di setiap jalur *input* rangkaian *multiplexer quad 2-line to 1-line* IC 74157.

### 1.7 Sistematika Penulisan

Untuk memudahkan penulisan dan pemahaman mengenai materi penelitian ini, maka tulisan ini akan dibagi menjadi lima, yaitu:

### BAB I. PENDAHULUAN

Pada bab ini memuat latar belakang perumusan masalah, tujuan penelitian, batasan masalah, manfaat penelitian, serta sistematika penulisan.

### BAB II TINJUAN PUSTUKA

Pada bab ini membahas tentang teori-teori dasar yang mendukung penelitian ini, yang diambil dari berbagai sumber ilmiah yang digunakan dalam laporan penelitian ini.

### **BAB III METODE PENELITIAN**

Pada bab ini menjelaskan waktu dan tempat penelitian, alat dan bahan yang digunakan dalam penelitian, metode penelitian yang digunakan, serta pelaksanaan dan pengamatan penelitian.

### BAB IV HASIL DAN PEMBAHASAN

Pada bab ini menjabarkan data hasil penelitian dan pembahasan hasil data yang telah diperoleh dari penelitian ini.

### BAB V KESIMPULAN

Pada bagian bab terakhir ini menjelaskan kesimpulan yang berdasarkan hasil data dan pembahasan yang mengacu pada tujuan penelitian.

### II. TINJAUAN PUSTAKA

### 2.1 Penelitian Terdahulu

Ketika melaksanakan penelitian dibutuhkan peninjauan terkait dengan penelitian yang telah dilaksanakan atau penelitian sebelumnya supaya menghasilkan referensi yang sesuai dengan penelitian yang sedang dilakukan saat ini, yaitu tentang pendeteksian gangguan pada rangkaian digital kombinasional. Berikut beberapa uraian terkait dengan penelitian terdahulu yang digunakan sebagai acuan penelitian ini:

Berdasarkan penelitian Ageng Sadnowo Repelianto pada tahun 1996 dalam penelitianya yang berjudul Penggunaan Metoda Tabel Kesalahan untuk Diagnosis Kesalahan Rangkaian Digital Kombinasional. Penelitian ini menggunakan metode tabel kesalahan untuk diagnosis kesalahan rangkaian kombinasional berdasarakan analisa kesalahan yang mungkin muncul pada rangkaian dan disusun dalam sebuah tabel kesalahan. Dihasilkan panjang eksperimen deteksi tanpa kesalahan adalah 10 tingkat pengujian dari 4096 variasi pengujian dengan efisiensi pengujian 99,76%. Lokasi kesalahan pada modul menghasilkan panjang ekperimen deteksi tanpa kesalahan adalah 11 tingkat pengujian dengan efesiensi sebesar 99,73%. Pohon diagnosa mempercepat ditemukannya lokasi kesalahan yang terjadi pada rangkaian. Deteksi kesalahan tunggal memiliki rata-rata panjang pengujian 5,258 tingkat pengujian atau mempunyai efesiensi sebesar 47,42% dari panjang pengujian tanpa kesalahannya. Deteksi kesalahan pada modul mempunyai rata-rata panjang pengujian adalah 5,35 tingkat pengujian atau mempunyai efesiensi sebesar 51,36% dari panjang pengujian tanpa kesalahannya [4].

Berdasarkan penelitian Akshay Baid dkk pada tahun 2013 yang berjudul Generating Test Patterns for Fault Detection in Combinational Circuits Using Genetic Algorithm. Penelitian ini bertujuan untuk pendeteksian kesalahan otomatis dan uji minimalisasi berdasarkan model kesalahan stuck-at pada produksi *chip* sebelum dipasarkan dan digunakan secara masal menggunakan algoritma genetika, pengujian ini dicapai dengan menghasilkan pola pengujian dalam cakupan kesalahan yang tinggi serta harus menjadikan rangkaian pengujian minimal untuk mengurangi biaya produksi dengan cara menghemat waktu produksinya. Cacat pada chip diasumsikan sebagai kesalahan tetap atau permanen yang bersifat tidak sementara, artinya tanpa diperbaiki atau diperbaiki kesalahan tersebut akan tetap ada. Rangkaian yang digunakan adalah rangkaian logika resistor transistor (RTL), rangkaian logika diode transistor (DTL) dan rangkaian logika transistor-transistor (TTL). Proses pengujian, menggunakan model kesalahan tunggal stuck-at, semua gangguan stuck-at 0 dan stuck-at 1 dalam sebuah rangkaian dapat dideteksi jika rangkaian tersebut tidak redundan serta fungsi yang direalisasikan adalah fungsi yang diminimalisasikan. Kesalahan tidak dapat dibedakan jika tabel kebenaran dari fungsi keluaran rangkaiannya adalah identik. Penerapan dilakukan dengan populasi awal 10 kromosom untuk rangkaian yang lebih kecil dan 25 kromosom untuk rangkaian yang lebih besar dihasilkan secara acak. Kemudian kesalahan disimulasikan dan dilihat apakah keluaran yang diperoleh berbeda dari respon bebas kesalahan. Algoritma genetika membantu menemukan dengan cepat kumpulan pola pengujian optimal yang dapat mendeteksi kesalahan pada sebuah rangkaian. Algortima ini dapat digunakan dalam generator pola pengujian otomatis untuk mendeteksi kesalahan yang diberikan dengan model stuck-at. Perbaikan lebih lanjut dapat dilakukan dengan menyertakan kesalahan tunda dan mengimplementasikan untuk rangkaian berurutan. Hasilnya untuk rangkaian benchmark ISCAS 1989 pada rangkaian C17 yang diberikan satu kesalahan yaitu pada jalur G10 stuck-at 0 didapatkan 6 iterasi cakupan kesalahan dari 100 cakupan kesalahan [8].

Berdasarkan penelitian Yu Zhang dkk pada tahun 2014 yang berjudul Diagnostic Test Generation for Transition Delay Faults Using Stuck-At Fault

Detection Tools. Penelitian ini bertujuan untuk meningkatkan kepadatan logika, kecepatan, dan waktu terhadap tekanan chip VLSI modern. Diagnosis kesalahan merupakan langkah yang penting dalam mengisolasi lokasi jaringan cacat produksi yang paling mungkin terjadi sehingga identifikasi dan eliminasi cacat produksi dapat dilakukan. Delay diagnosis kesalahan merupakan karakteristik penting kinerja perangkat VLSI modern dan cakupan diagnostik yang tinggi dari pengujian yang diinginkan. Menambahkan beberapa gerbang logika dengan satu atau dua model flip-flop ke rangkaian yang diuji. Membuat model deteksi atau generator pola diagnosis uji otomatis dari model kesalahan tunda transisi yang dapat digunakan oleh generator pola uji kesalahan tunggal stuck-at konvensional. Metode yang digunakan yaitu kesalahan penundaan transisi.Model generator pola diagnosis uji otomatis dapat diperluas menjadi dua kerangka waktu untuk memfasilitasi penggunaan generator pola diagnosis uji otomatis kombinasional. Waktu yang dihasilkan pada rangkaian yang diuji adalah 14841 detik untuk 1645 percobaan ekslusif. Percobaan ini menemukan bahwa hampir 99,8% waktu dihabiskan dalam rekonstruksi struktur data. Waktu yang dibutuhkan untuk proses pembuatan uji diagnostik akan berkurang menjadi beberapa menit untuk rangkaian besar dan detik untuk rangkaian kecil. Akibatnya, presentase pasangan kesalahan penundaan transisi yang berbeda lebih besar dan sistem pembangkitan uji ekslusif otomatis yang diusulkan lebih efesien waktu [9].

Berdasarkan penelitian Ashwani Kumar dkk pada tahun 2016 yang berjudul *Transistor Level Fault Diagnosisin Digital Circuits Using Artificial Neural Network.* Jaringan syaraf tiruan dalam penelitian ini diaplikasikan untuk diagnosis kesalahan pada rangkaian digital, gangguan level transistor terjadi karena korsleting di terminal transistor dengan variasi parameter transistor. Selama proses diagnosis, variasi parametrik dalam transistor juga diperhitungkan dengan memvariasikan tegangan ambang transistor. Jaringan syaraf tiruan yang digunakan dalam klasifikasi kesalahan pada gebang NAND menggunakan 25 neuron lapisan tersembunyi. Terdapat 462 periode jaringan syaraf tiruan yang dilatih. Jaringan syaraf tiruan yang digunakan untuk klasifikasi kesalahan pada rangkaian gerbang NOR menggunakan 30 *neuron*

lapisan tersembunyi dan dilatih dalam 452 periode. Semua model kesalahan yang ditentukan terdiagnosis dengan benar, menghasilkan efisiensi diagnosis yang sama seperti yang diperoleh pada rangkaian gerbang NAND [10].

Berdasarkan penelitian Soham Roy dkk pada tahun 2021 dengan judul Training Neural Network for Machine Intelligence in Automatic Test Pattern Generator. Penelitian ini menunjukkan bahwa jaringan syaraf tiruan dapat menggabungkan beberapa heuristic untuk memandu generator pola pengujian otomatis dengan backtrack lebih sedikit daripada yang dibutuhkan oleh panduan dari heuristic tunggal manapun. Metode yang digunakan yaitu dengan mengembangkan metode pelatihan baru untuk memasukan beberapa heuristik. Jaringan syaraf tiruan memiliki neuron keluaran tunggal dan satu lapisan neuron tersembunyi, yang cukup untuk mengkomodasi volume data pelatihan. Generator pola pengujian otomatis konvensional diterapkan pada kesalahan yang sulit dideteksi dan mudah dideteksi pada rangkaian benchmark yang dipilih memberikan data pelatihan untuk node yang ditandai sebagai "sukses". Jika backtrace mengarah ke pengujian dan "gagal" jika menghasilkan backtrack. Eksperimen menggunakan semua kesalahan untuk menunjukkan keakuratan jaringan syaraf tiruan menggunakan teknik pelatihan yang diusulkan. Pengamatan penting yang dilakukan yaitu pada C17, B02, dan B01 tidak memiliki fanout konvergen sehingga tidak memiliki backtrack. Tidak ada ruang untuk mengurangi backtrak dengan panduan JST baru. Jumlah backtrace adalah konstan atau berkurang dalam rangkaian bebas fanout rekonvergen ini oleh JST baru kecuali pada C1908, C432, C499, dan B05. Berdasarkan tabel data hasil yang menunjukkan waktu komputasi generator pola uji otomatis "CPU Time (ms)", "Backtrace Count", dan "Backtrack Count". Jaringan syaraf tiruan baru bekerja lebih baik dengan backtracks lebih sedikit dari jaringan syaraf tiruan aslinya [5].

Berdasarkan penelitian Isha Gupta pada tahun 2022 yang berjudulkan *Stuck at Fault Testing in Combinational Circuit Using FPGA*. Pendekatan berbasis FPGA untuk generator pola pengujian dan pengujian rangkaian kombinasional. Konsep emulasi disajikan untuk mendeteksi kesalahan dalam rangkaian

menggunakan perangkat keras FPGA. Permasalahan sedikitnya port masukan dan keluaran yang tersedia pada papan FPGA telah diatasi melalui pendekatan multiplexing sakelar. Papan FPGA yang digunakan pada penelitian ini adalah papan pengembangan berbasis Spartan 6 FPGA yang dikembangkan oleh CDAC Noida. Modul rangkaian benchmark C17 tanpa kesalahan dikodekan di Verilog. Kemudian dua Salinan tambahan dari modul C17 yang sama dibuat multiplexer dan dimasukan pemeriksaan untuk injeksi kesalahan berdasarkan jalur yang dipilih. Hal yang sama diterapkan pada papan FPGA berbasis Spartan 6, masukan diberikan melalui sakelar dan tombol. Terdapat 12 sakelar akan dipetakan ke 12 masukan dan proses akan diulangi tergantung dengan jumlah total masukan yang akan diberikan. Dengan demikian finite state machine diimplementasikan untuk memetakan prilaku transisi, kondisi ini yang dapat mengetahui berapa kali tombol telah ditekan. Setelah semua masukan telah diberikan, keluaran dieksekusi dan kesalahan dapat dideteksi. Keluaran diteruskan melalui LED pada papan FPGA. Keluaranya adalah EXOR dari keluaran yang diperoleh pada rangkaian bebas kesalahan dan rangkaian yang rusak. Setiap kali LED menyala, menggambarkan bahwa keluaran yang diperoleh berbeda, ini menyiratkan bahwa kesalahan telah mengubah hasil keluaran. Pengujian ini menghasilkan persentase pemanfaatan untuk irisan register, LUT dan angka sebagai logika sebesar 1%,3%, dan 3%. Persentase jumlas irisan dan jumlah MUXCY yang digunakan adalah 4% [11].

Secara garis besar, penelitian-peneltian terdahulu memiliki kelebihan dan kekurangnya masing-masing. Berdasarkan penelitian ini melalui metode yang telah ditentukan diharapakan dapat memberikan informasi penting untuk kemajuan dunia industri digital dan mikrokomponen. Keuntungan yang ditawarkan pada penelitian ini adalah penggunaan komponen dan metode yang lebih sederhana sehingga lebih efisien dan cepat dalam mendeteksi kesalahan pada rangkaian digital kombinasional.

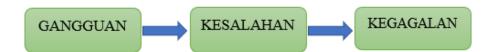

### 2.2 Gangguan Digital

Gangguan merupakan sebuah kerusakan yang berbentuk fisik. Cacat yang biasa terjadi pada komponen-komponen dalam peralatan elektronika, baik pada perangkat lunak maupun perangkat keras. Gangguan sendiri bisa berbentuk sebuah kesalahan, seperti penyimpangan yang terjadi dari hasil sebenarnya pada sebuah fungsi rangkaian. Berdasarkan perancangan toleransi gangguan, gangguan terdiri dari tiga bentuk dasar yaitu, gangguan, kesalahan, dan kegagalan. Ketiga bagian tersebut memiliki hubungan yang saling berkaitan [6]. Gangguan merupakan penyebab terjadinya kesalahan serta kesalahan merupakan penyebab dari terjadinya kegagalan suatu sistem rangkaian elektronika [2].

Apabila hasil dari suatu kesalahan yang memiliki fungsi tidak sesuai dalam sebuah sistem, maka akan terjadi sebuah kegagalan pada sistem tersebut [12]. Sehingga kegagalan merupakan perbuatan yang bukan sifat sebenarnya dari sebuah sistem, seperti pada Gambar 2.1.

Gambar 2.1 Ikatan antara Gangguan, Kesalahan, dan Kegagalan

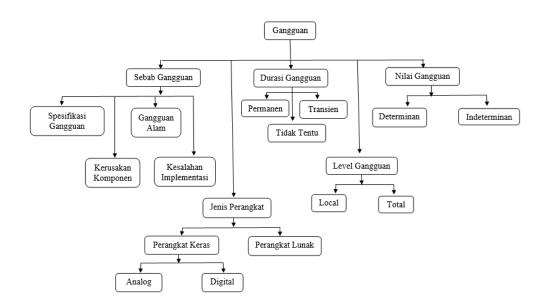

### 2.3 Karakteristik Gangguan

Karakteristik gangguan terdiri dari beberapa aspek, salah satunya yaitu dari segi durasi atau lamanya gangguan terjadi. Gangguan permanen merupakan karekteristik gangguan yang tidak akan hilang apabila tidak ditangani dengan cepat, akibat yang akan ditimbulkan yaitu sistem kerja dari rangkaian logika tidak bisa bekerja dengan baik, sehingga perangkat elektronika tersebut rusak dan tidak akan bisa digunakan [6]. Adapun contoh dari jenis karakterisktik gangguan permanen, yaitu terjadinya kerusakan jalur atau gerbang logika yang

disebabkan oleh kerusakan fisik komponen pada perangkat elektronika atau karena dari jalur gerbang logika perangkat itu sendiri.

Gangguan transien merupakan karakteristik gangguan yang timbul dan dapat menghilang dalam jeda waktu tertentu [13]. Salah satu contoh gangguan transien yaitu gangguan yang disebabkan dari faktor luar seperti halilintar. Halilintar dapat menyebabkan gangguan sebuah sistem dalam jangka waktu tertentu, namun tidak merusaknya. Setelah halilintar menghilang maka gangguan transien juga menghilang [3]. Gangguan tidak menentu merupakan salah satu gangguan yang bisa muncul, menghilang dan kemudian muncul kembali secara berulang-ulang. Jenis karakteristik gangguan seperti Gambar 2.2.

Gambar 2.2 Karakteristik Gangguan

### 2.4 Gerbang Logika

Gerbang-gerbang logika utama merupakan sebuah elemen dasar yang dibentuk menjadi sebuah rangkaian digital yang mempunyai kesatuan dari beberapa gerbang-gerbang logika dasar yang bentuknya berfungsi untuk memproses sinyal digital [14]. Gerbang logika umumnya terdiri atas tiga gerbang utama diantaranya, gerbang NOT, Gerbang AND dan gerbang OR [1]. Adapun

gerbang lain selain gerbang utama yaitu seperti gerbang NAND, gerbang NOR, gerbang XOR dan gerbang XNOR merupakan kombinasi dari tiga gerbang logika utama tersebut [4].

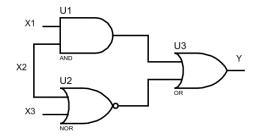

### 2.5 Rangkaian Kombinasional

Rangkaian gabungan atau yang biasa disebut dengan rangkaian kombinasional merupakan sebuah rangkaian yang memiliki besaran keluaranya (output) bergantung pada besaran masukannya (input) [15]. Prinsip kerja dari rangkaian kombinasional memiliki nilai pada keluaranya yang ditetapkan berdasarkan besaran masukannya pada waktu tertentu, hal ini dikarenakan rangkaian kombinasional tidak mempunyai karakter memori. Beberapa contoh pengaplikasian dari rangkaian digital kombinasional diantaranya, adder, komperator, Demultiplexer, multiplexer, decoder dan encoder [1]. Rangkaian digital kombinasional yang irendundan terjadi akibat kesalahan logika yang terjadi pada setiap bagian dari rangkaian yang akan menyebabkan perubahan dalam fungsi penyambungan yang diwujudkan oleh rangkaian bebas kesalahan tersebut [9].

Proses kerja rangkaian digital kombinasional menggunakan prinsip aljabar Boolean. Aljabar Boolean merupakan perpaduan dari salah satu aljabar matematika yang mempunyai nilai kebenaran yaitu *true* dan *false* nilai kesalahan [14]. Nilai kebenaran dilambangkan dengan angka 1 dan nilai kesalahan dilambangkan dengan angka 0. Boolean disebut juga dengan aljabar biner yang hanya mengenal dua masukan yaitu 0 dan 1. Aljabar Boolean dikenal juga untuk digunakan dalam menganalisa dan menyederhanakan rangkaian digital atau gerbang logika [15]. Berdasarkan Gambar 2.4 didapatkan persamaan Boolean 2.1.

$$Y = f(X_1, X_2, X_3) = X_1 X_2 + (\overline{X2 + X3})$$

(2.1)

Gambar 2.3 Rangkaian Digital Kombinasional

### 2.6 Diagnosa Kesalahan

Diagnosa kesalahan merupakan proses pendeteksian kesalahan serta mencari letak terjadinya kesalahan. Mendiagnosa kesalahan dibutuhkan sebuah set pengujian, yaitu sebuah set minimal yang dapat mendeteksi masing-masing kesalahan yang sedang diteliti [4]. Penyusunan set pengujian deteksi kesalahan minimal untuk rangkaian digital kombinasional dibutuhkan set pengujian lengkap dari setiap kesalahan yang sedang diteliti [8]. Sebuah pengujian kesalahan dapat diartikan sebagai aplikasi dari sebuah pola masukan pada masukan utama dan pemantaun pada keluaran utama sehingga adanya kesalahan bisa dideteksi dengan sebuah set pengujian lengkap dari sebuah kesalahan yang berisi semua pengujian kesalahan.

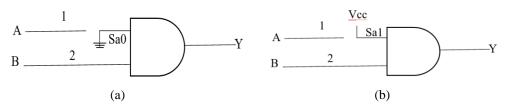

### 2.7 Model Gangguan Stuck Logika

Penerapan model gangguan *stuck* logika sangat bervariasi dan sangat luas karena model ini sangat sederhana dan efektif penggunanya. Model gangguan ini bisa sebagai gangguan *stuck at* 0 (Sa0) atau sebagai gangguan *stuck at* 1 (Sa1) [4].

Gambar 2.4 Konsep dasar Model Gangguan *Stuck* Logika (a) Stuck at 0, (b) Stuck at 1

Secara sederhana gangguan pada suatu rangkaian digital dimodelkan menjadi kesalahan logika *stuck*, masukan gerbang mengalami *stuck at* 1 (Sa1) atau *stuck at* 0 (Sa0) yang analoginya bisa dilihat pada Gambar 2.3. Sa1 adalah kondisi seolah-olah *input* gerbang mengalami situasi selalu terhubung logika 1 meskipun *input* A bernilai 1 ataupun 0. Sementara itu, Sa0 kondisi dimana *input* gerbang terkondisi pada logika 0, meskipun *input* a bernilai 1 atau 0 [17].

Tabel 2.1 Keluaran Gerbang AND saat Normal dan Dalam Kondisi Stuck

| Uji | В | A | $y_0$ | $y_{10}$ | $y_{11}$ | $y_{20}$ | $y_{21}$ |

|-----|---|---|-------|----------|----------|----------|----------|

| 0   | 0 | 0 | 0     | 0        | 0        | 0        | 0        |

| 1   | 0 | 1 | 0     | 0        | 0        | 0        | 1        |

| 2   | 1 | 0 | 0     | 0        | 1        | 0        | 0        |

| 3   | 1 | 1 | 1     | 0        | 1        | 0        | 1        |

Tabel 2.1 menunjukkan kondisi gerbang AND dalam kondisi normal  $y_0$ , dan kondisi jalur input A dan B mengalami gangguan Sa0 dan Sa1 berturut-turut  $y_{10}$ ,  $y_{11}$ ,  $y_{20}$  dan  $y_{21}$ . Pola output yang sama terlihat pada  $y_{10}$  dan  $y_{20}$ , kedua pola tidak dapat dibedakan oleh set uji [17]. Dengan demikian kedua kondisi dikelompokkan dalam satu pola kesalahan  $f_1$  seperti pada tabel 2. Secara lengkap terdapat 4 kelompok kesalahan.  $f_0$  adalah pola output tanpa kesalahan. Kemudian  $f_1$  adalah pola output yang menunjukkan adanya gangguan di lokasi jalur 1 atau jalur 2 mengalami Sa0.  $f_2$  adalah pola output dengan gangguan di lokasi jalur 1 mengalami Sa1. Terakhir  $f_3$  adalah pola output yang menunjukkan gangguan di lokasi jalur 2 dengan Sa1 [4].

Tabel 2.2 Lokasi Kesalahan Gerbang *AND* Saat Normal dan Dalam Kondisi *Stuck*.

| Uji | В | A | $f_0 = \{y_0\}$ | $f_1 = \{y_{10}, y_{20}\}$ | $f_2 = \{y_{11}\}$ | $f_3 = \{y_{21}\}$ |

|-----|---|---|-----------------|----------------------------|--------------------|--------------------|

| 0   | 0 | 0 | 0               | 0                          | 0                  | 0                  |

| 1   | 0 | 1 | 0               | 0                          | 0                  | 1                  |

| 2   | 1 | 0 | 0               | 0                          | 1                  | 0                  |

| 3   | 1 | 1 | 1               | 0                          | 1                  | 1                  |

Pada Tabel 2.2 pengujian (0) adalah redundan yang tidak dapat membedakan kesalahan karena tidak ada hasil ketika menggunakan operasi X-OR, sehingga pengujian {1, 2, 3} adalah set pengujian lengkap minimal untuk gerbang *AND*.

Tabel 2.3 Pemilihan Set Pengujian Lengkap

| X-OR Set Kesalah |   |   |   |   |   |   |   | ha | n |

|------------------|---|---|---|---|---|---|---|----|---|

| Uji              | £ | 0 | 0 | 0 | t | 1 | 1 | £  | 2 |

|                  | 1 | 1 | 2 | 3 | 1 | 2 | 3 | 1  | 3 |

| 0                |   |   |   |   |   |   |   |    |   |

| 1                |   |   |   | 1 |   |   | 1 |    | 1 |

| 2                |   |   | 1 |   |   | 1 |   |    |   |

| 3                |   | 1 |   |   |   | 1 | 1 |    |   |

Keterangan:  $f_{ab} = f_a X$ -OR  $f_b$

### 2.8 Pohon Diagnosa

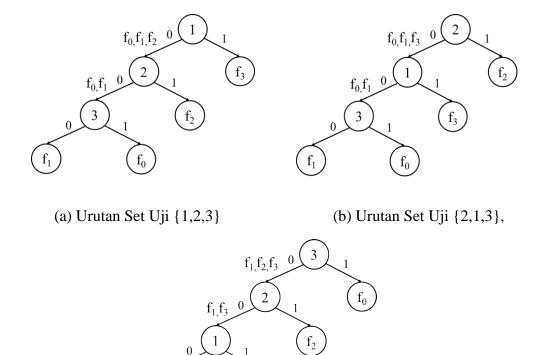

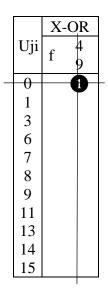

Pohon diagnosa merupakan sebuah grafik penunjuk yang mempunyai simpul berupa pengujian. Cabang yang dihasilkan dari simpul-simpul menyatakan akibat yang berbeda dari pengujian khusus. Masing-masing cabang menyatakan kesalahan-kesalahan yang mungkin ada didalam rangkaian tersebut. akar cabang dari pohon diagnosa memberikan petunjuk apakah rangkaian bebas dari kesalahan atau ada kemungkinan terjadinya kesalahan [4]. Selanjutnya, menentukan urutan variabel uji untuk membentuk pohon diagnosa. Langkah pertama, menentukan selisih jumlah 0 dan 1 dalam setiap baris. Tujuan Ri untuk menyeimbangkan jumlah 0 dan 1 supaya cepat dicarinya sehingga selisih yang paling kecil dipilih sebagai uji yang terdahulu. Untuk mencari Ri menggunakan persamaan 2.2 sebagai berikut:

$$Ri = |wi_0 - wi_1|$$

(2.2)

Dimana: Ri merupakan selisih terkecil antara jumlah 0 dan 1 wi<sub>0</sub> adalah jumlah dari 0 wi<sub>1</sub> adalah jumlah dari 1

Gambar 2.5 merupakan baris uji 1, 2 dan 3 yang memiliki selisih jumlah 0 dan 1 yang sama, yaitu 2. Oleh karenanya, sebagai variabel uji pertama dapat dipilih 1, 2 atau 3. Jika uji 1 yang dipilih, dan *output* menghasilkan 1, pengujian sudah dapat mengenali bahwa gerbang mengalami gangguan di lokasi dengan definisi  $f_3$ . Namun jika *output*nya 0, hal ini mengindikasikan gerbang dalam kondisi  $f_0$ ,

$f_1$ , atau  $f_2$ . Kemudian, usaha yang sama dilakukan agar  $f_0$ ,  $f_1$ , atau  $f_2$  dapat dibedakan.

Gambar 2.5 Menentukan Urutan Set Uji Pohon Diagnosa

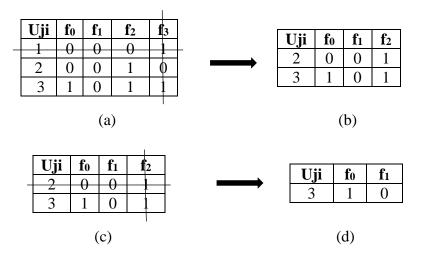

Langkah kedua mengecilkan matrik pencarian dengan menghilangkan komponen bernilai 1 yang dalam kekuasaan kolom terhadap baris seperti pada tabel 3(a) dan membentuk tabel 3(b). Terdapat komponen uji 2 dan 3. Pilih salah satu diantaranya dengan melakukan langkah pertama. Kedua komponen uji memiliki selisih jumlah 0 dan 1 yang sama, karenanya, dapat dipilih uji 2 atau uji 3 sebagai set uji ke dua. Jika uji 2 yang dipilih keluaran gerbang AND yang bernilai 1 akan mendeteksi adanya gangguan di lokasi dengan kondisi kesalahan f<sub>2</sub>. Selanjutnya Pengujian dengan set uji 3, akan membedakan kondisi gerbang dalam kondisi baik f<sub>0</sub> jika *output* gerbang bernilai 1, atau mengindikasikan gerbang dalam gangguan dengan kondisi f<sub>1</sub> [5]. Urutan pengujian ini digambarkan dalam sebuah pohon diagnosa bisa dilhat pada Gambar 2.6(a). Gambar 2.6(b) dan 2.6(c) adalah alternatif prioritas set uji.

(c) Urutan Set Uji {3,2,1}

Gambar 2.6 Pohon Diagnosa Gerbang AND

Hasil dari pohon diagnosa pada Gambar 2.5 diimplementasikan menjadi sebuah generator set uji [17]. Efisiensi yang dihasilkan oleh generator set uji didapatkan dengan persamaan sebagai berikut [4]:

Efesiensi (%) =

$$\frac{2^{n} - Level \ Pengujian \ Set \ Kesalahan}{2^{n}} x \ 100 \qquad (2.3)$$

Dimana: *n* adalah jumlah *input* rangkaian uji

### III. METODE PENELITIAN

# 3.1 Waktu dan Tempat Penelitian

Penelitian dan perancangan tugas akhir ini dilaksanakan dari bulan Agustus 2022 sampai Juni 2023, bertempat di Laboratorium Terpadu Teknik Elektro, Jurusan Teknik Elektro, Universitas Lampung.

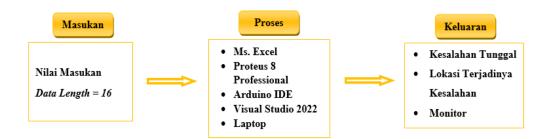

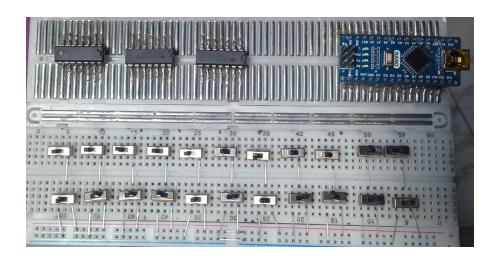

#### 3.2 Alat dan Bahan Penelitian

Adapun alat dan bahan pada penelitian tentang rancang bangun generator tes ini adalah sebagai berikut:

- 1. 1 Unit Laptop Asus

- 2. Software GUI

- 3. 8 Buah Project Board

- 4. 1 Buah Arduino Nano

- 5. 1 Buah Ic 74157

- 6. 4 Buah Ic 7411 (AND)

- 7. 4 Buah Ic 7432 (*OR*)

- 8. 4 Buah Ic 7414 (*NOT*)

- 9. 88 Buah Sakelar SPDT

- 10. 1 Buah Multimeter

#### 3.3 Prosedur Penelitian

Metode penelitian yang digunakan dalam penelitian ini *Research and Development*. (R&D). Penelitian serta pengembangan merupakan metode penelitian yang digunakan untuk menghasilkan serta mengembangkan suatu produk dan menguji validitas produk yang dihasilkan.

Pada penelitian ini didapatkan set pengujian lengkap menggunakan metode tabel kesalahan yang dipetakan menjadi pohon diagnosa. Pohon diagnosa diimplemntasikan menjadi generator set uji yang menghasilkan efisiensi waktu dalam mendiagnosis kesalahan pada rangkaian kombinasional.

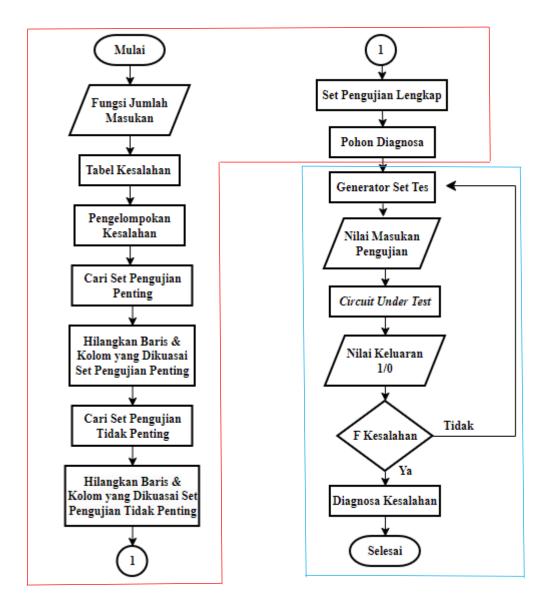

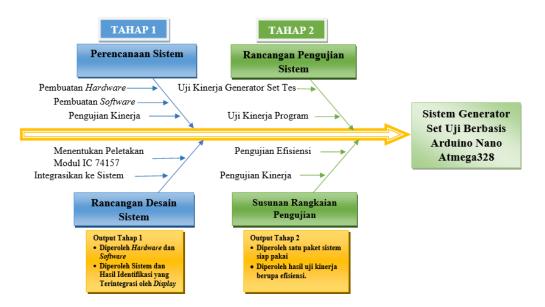

### 3.4 Metode yang Digunakan

Secara keseluruhan tahapan penelitian dibuat dalam bentuk diagram alir dan diagram tulang ikan. Diagram alir perancangan generator set uji tersusun dari dua bagian utama. Bagian pertama yang ditandai dalam garis merah adalah penurunan set uji yang dipetakan pada pohon diagnosa. Bagian kedua yang ditandai dalam garis biru adalah implementasi pohon diagnosa menjadi sebuah generator set uji. Perancangan tersebut bisa dilihat pada Gambar 3.1.

Diagram tulang ikan menjelaskan tahapan yang dilakukan dengan rinci pada penelitian ini, dapat diliihat pada Gambar 3.2.

Gambar 3.1 Diagram Alir Perancangan Generator Set Uji

# Tahap 1

Perancanaan sistem, pada proses ini dilaksanakan perancangan *hardware* dan *software* lalu melakukan pengujian kinerja. Sehingga diperoleh sistem yang diinginkan. Komponen sistem yang dirancang terdiri dari Arduino Nano Atmega328, IC 7408 (gerbang *AND*), IC 7432 (gerbang *OR*), IC 7414 (gerbang *NOT*) dan saklar SPDT 3 posisi.

Perancangan *display* hasil identifikasi, pada proses ini dilaksanakan perancangan skematik, *display* diintegrasikan dengan sistem lalu melakukan pengujian kinerja sistem. Hasil diagnosis kesalahan pada sistem generator set tes akan ditampilkan menggunakan *software* GUI melalui layar laptop. Pada tahap ini didapatkan hasil yaitu berupa rancangan *hardware* dan *software* yang terintegrasi dengan sistem dan *display* hasil diagnosa kesalahan generator set tes menggunakan *software* GUI.

### Tahap 2

Pengujian kinerja serta akurasi sistem secara keseluruhan, proses ini adalah proses akhir pada perancangan sistem, pengujian kinerja yaitu akurasi dan stabilitas. Pengujian dilakukan dengan cara menggunakan susunan modul-modul IC menjadi rangkaian *multiplexer quad* 2 *line to* 1 *line* IC 74157 dalam kondisi nyata. Desain pengujian sama dengan pengujian lapangan awal dengan menggunakan metode eksperimen. Bila pengujian generator set tes belum memenuhi spesifikasi sesuai dengan yang diinginkan, maka perlu ada revisi terhadap produk tersebut. Hasil revisi selanjutnya digunakan untuk pengujian lapangan operasional. Pengujian lapangan operasional dilakukan dengan cara menguji sistem pengontrolan diantaranya identifikasi dan karakterisasi IC 74157. Tahapan ini diharapkan menghasilkan data akurat dari sistem pengontrol generator set tes.

Gambar 3.2 Diagram Tulang Ikan Tahapan Penelitian

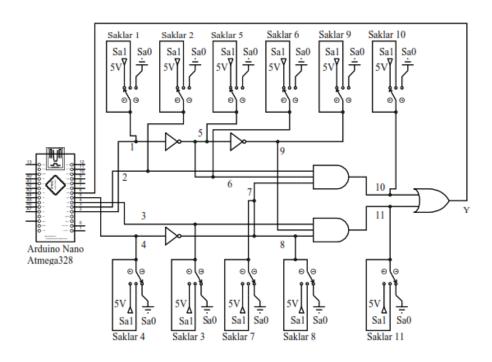

# 3.5 Susunan Rangkaian Pengujian

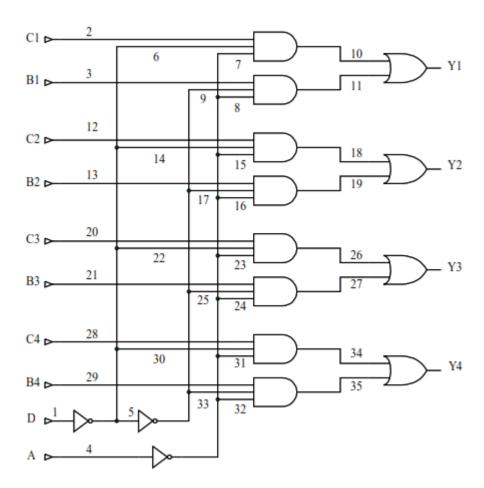

Sebagai aplikasi yang akan dicontohkan penyelesaian untuk penurunan eksperimen pengujian kesalahan dengan menggunakan rangkaian *multiplexer* quad 2 line to 1 line IC 74157. Rangkaian ini terdiri dari 15 gerbang logika yaitu tiga gerbang *NOT*, delapan gerbang *AND* dan empat gerbang *OR* dan 35 jalur masukan.

Gambar 3.3 Rangkaian Multiplexer Quad 2 Line to 1 Line IC 74157

Untuk mempermudah penurunan pengujian dilakukan penamaan untuk semua gerbang masukan dan jalur keluaran.

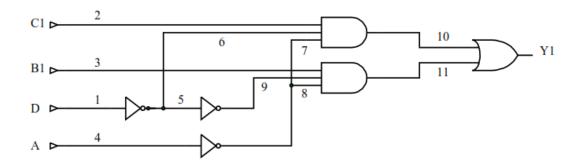

Gambar 3.4 Penyederhanaan Rangkaian untuk Penurunan Pengujian

Dalam menyusun tabel kesalahan untuk deteksi semua kesalahan tunggal dari rangkaian kombinasional perlu diperhatikan fungsi keluaranya seperti persamaan Boolean 2.1. Fungsi keluaran dari rangkaian Gambar 3.4, yaitu:

$$Y_1 = \overline{A}C1\overline{D} + \overline{A}B1D \tag{3.1}$$

Rangkaian multiplexer IC 74157 dapat disederhanakan menjadi empat potongan rangkaian uji karena memiliki pola yang sama. Persamaan boolean 3.1 dihasilkan dari potongan rangkaian uji pertama seperti Gambar 3.4.

Jika rangkaian IC 74157 Gambar 3.3 dipotong seperti Gambar 3.4 maka di hasilkan persamaan untuk potongan ke-2, ke-3 dan ke-4 dari rangkaian multiplexer IC 74157 adalah sebagai berikut:

$$Y_2 = \overline{A}C2\overline{D} + \overline{A}B2D \tag{3.2}$$

$$Y_3 = \overline{A}C3\overline{D} + \overline{A}B3D \tag{3.3}$$

$$Y_4 = \overline{A}C4\overline{D} + \overline{A}B4D \tag{3.4}$$

Persamaan di atas didapatkan karena input yaitu B2, C2 dengan keluaran  $Y_2$  dan B3, C3 dengan keluaran  $Y_3$  serta B4 dan C4 dengan keluaran  $Y_4$  memiliki pola yang identik dengan masukan B1, C1 dengan keluaran  $Y_1$ .

Tabel 3.1 Tabel Kebenaran IC 74157

| No |   | Mas | ukan |   | Keluaran |

|----|---|-----|------|---|----------|

| No | D | C   | В    | A | y        |

| 1  | X | X   | X    | Н | L        |

| 2  | L | L   | X    | L | L        |

| 3  | L | Н   | X    | L | Н        |

| 4  | Н | X   | L    | L | L        |

| 5  | Н | X   | Н    | L | Н        |

Keterangan: L = Low, H = High, dan X = Tidak ada

### 3.6 Metode Tabel Kesalahan

Metode tabel kesalahan adalah metode untuk mendeteksi dan memetakan kesalahan logika permanen atau kesalahan tunggal dalam suatu rangkaian digital kombinasional. Metode tabel kesalahan menurunkan set pengujian yang didapatkan dengan membandingkan tabel kebenaran dari rangkaian normal dan rangkaian yang mengalami kesalahan. Dalam penurunan panjang sebuah set pengujian, penjadwalan pengujian tidak bergantung pada hasil urutan pengujian tersebut.

# 3.6.1 Penyusunan Tabel Kesalahan

Gangguan pada rangkaian Gambar 3.4 dimodelkan dengan kesalahan  $logic\ stuck$  pada setiap jalur masukannya. Masukan gerbang mengalami  $stuck\ at\ 1\ (Sa1)$  atau  $stuck\ at\ 0\ (Sa0)$ . Rangkaian Gambar 3.4 dalam kondisi normal atau tanpa adanya kesalahan yaitu  $y_0$ , serta kondisi jalur  $input\ A$ , B1, C1 dan D mengalami gangguan Sa0 dan Sa1 berturut-turut pada potongan rangkaian pertama IC 74157. Hasil keluaran potongan rangkaian pertama didapatkan menggunakan Persamaan 3.1 yang bisa dilihat pada Tabel 3.2.

Tabel 3.2 Tabel Kesalahan Diagnosa Semua Kesalahan Tunggal dari Rangkaian 1

|    |   | Ma | sukar | 1  |   |    |    |    |    |    |    |    |    |    | Ni | lai Ke | eluara | ın |    |    |    |    |    |     |     |     |     |

|----|---|----|-------|----|---|----|----|----|----|----|----|----|----|----|----|--------|--------|----|----|----|----|----|----|-----|-----|-----|-----|

| U  | D | С  | B1    | A1 | y | у  | у  | у  | у  | у  | у  | у  | У  | y  | у  | у      | у      | y  | У  | у  | у  | у  | у  | у   | у   | у   | у   |

| 0  | 0 | 0  | 0     | 0  | 0 | 10 | 11 | 20 | 21 | 30 | 31 | 40 | 41 | 50 | 51 | 60     | 61     | 70 | 71 | 80 | 81 | 90 | 91 | 100 | 101 | 110 | 111 |

| 0  | 0 | 0  | Ů     | 0  | 0 | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1   | 0   | 1   |

| 1  | 0 | 0  | 0     | 1  | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1   | 0   | 1   |

| 2  | 0 | 0  | 1     | 0  | 0 | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1      | 0      | 0  | 0  | 0  | 0  | 0  | 1  | 0   | 1   | 0   | 1   |

| 3  | 0 | 0  | 1     | 1  | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1   | 0   | 1   |

| 4  | 0 | 1  | 0     | 0  | 1 | 1  | 0  | 0  | 1  | 1  | 1  | 1  | 0  | 0  | 1  | 0      | 1      | 0  | 1  | 0  | 1  | 1  | 1  | 0   | 1   | 1   | 1   |

| 5  | 0 | 1  | 0     | 1  | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0      | 0      | 0  | 1  | 0  | 1  | 0  | 0  | 0   | 1   | 0   | 1   |

| 6  | 0 | 1  | 1     | 0  | 1 | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 1      | 1      | 0  | 1  | 0  | 1  | 1  | 1  | 0   | 1   | 1   | 1   |

| 7  | 0 | 1  | 1     | 1  | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0      | 0      | 0  | 1  | 0  | 1  | 0  | 0  | 0   | 1   | 0   | 1   |

| 8  | 1 | 0  | 0     | 0  | 0 | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1   | 0   | 1   |

| 9  | 1 | 0  | 0     | 1  | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1   | 0   | 1   |

| 10 | 1 | 0  | 1     | 0  | 1 | 0  | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 1      | 0      | 0  | 1  | 0  | 1  | 0  | 1  | 1   | 1   | 0   | 1   |

| 11 | 1 | 0  | 1     | 1  | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0      | 0      | 0  | 1  | 0  | 1  | 0  | 0  | 0   | 1   | 0   | 1   |

| 12 | 1 | 1  | 0     | 0  | 0 | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0      | 1      | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1   | 0   | 1   |

| 13 | 1 | 1  | 0     | 1  | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1   | 0   | 1   |

| 14 | 1 | 1  | 1     | 0  | 1 | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 1      | 1      | 0  | 1  | 0  | 1  | 0  | 1  | 1   | 1   | 0   | 1   |

| 15 | 1 | 1  | 1     | 1  | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0      | 0      | 0  | 1  | 0  | 1  | 0  | 0  | 0   | 1   | 0   | 1   |

Keterangan : U adalah Pengujian,  $y_{x0}$  adalah Sa0 pada jalur x dan  $y_{x1}$  adalah Sa1 pada jalur x

Berdasarkan Tabel 3.2 didapatkan 10 kelompok kesalahan tunggal  $f_x$  dengan tujuh kelompok kesalahan memiliki pola keluaran yang sama yaitu  $\{y_{10}, y_{51}, y_{61}\}$  dikelompokan sebagai  $f_1$ ,  $\{y_{11}, y_{50}, y_{60}\}$  dikelompokan sebagai  $f_2$ ,  $\{y_{20}, y_{100}\}$  dikelompokan sebagai  $f_3$ ,  $\{y_{30}, y_{90}, y_{110}\}$  menjadi kelompok  $f_5$ ,  $\{y_{40}, y_{71}, y_{81}\}$  sebagai kelompok  $f_7$ ,  $\{y_{41}, y_{70}, y_{80}\}$  menjadi kelompok  $f_8$ , dan  $\{y_{101}, y_{111}\}$  menjadi kelompok  $f_{10}$  serta tiga kelompok kesalahan yang memiliki pola keluaran yang berbeda yaitu  $\{y_{21}\}$  sebagai kelompok  $f_4$ ,  $\{y_{31}\}$  sebagai  $f_6$ , dan  $\{y_{91}\}$  menjadi  $f_9$  seperti yang ditunjukkan pada Tabel 3.3

Tabel 3.3 Kelompok Kesalahan Potongan Rangkaian Uji Pertama

|     | $f_0$ | $f_1$           | $f_2$    | $f_3$     | $f_4$    | $f_5$                   | $f_6$           | $f_7$                  | f <sub>8</sub> | f9              | f <sub>10</sub> |

|-----|-------|-----------------|----------|-----------|----------|-------------------------|-----------------|------------------------|----------------|-----------------|-----------------|

| Uji | $y_0$ | $y_{10}$        | $y_{11}$ | $y_{20}$  | $y_{21}$ | $y_{30}$                | y <sub>31</sub> | $y_{40}$               | $y_{41}$       | y <sub>91</sub> | $y_{101}$       |

| - 3 |       | $y_{51}$        | $y_{50}$ | $y_{100}$ |          | $y_{90}$                |                 | <i>y</i> <sub>71</sub> | $y_{70}$       |                 | $y_{111}$       |

|     | 0     | y <sub>61</sub> | $y_{60}$ | 0         | 1        | <i>y</i> <sub>110</sub> | 0               | y <sub>81</sub>        | $y_{80}$       | 0               | 1               |

| 0   | 0     | 0               | 0        | 0         | 1        | 0                       | 0               | 0                      | 0              | 0               | 1               |

| 1   | 0     | 0               | 0        | 0         | 0        | 0                       | 0               | 0                      | 0              | 0               | 1               |

| 2   | 0     | 0               | 1        | 0         | 1        | 0                       | 0               | 0                      | 0              | 1               | 1               |

| 3   | 0     | 0               | 0        | 0         | 0        | 0                       | 0               | 0                      | 0              | 0               | 1               |

| 4   | 1     | 1               | 0        | 0         | 1        | 1                       | 1               | 1                      | 0              | 1               | 1               |

| 5   | 0     | 0               | 0        | 0         | 0        | 0                       | 0               | 1                      | 0              | 0               | 1               |

| 6   | 1     | 1               | 1        | 0         | 1        | 1                       | 1               | 1                      | 0              | 1               | 1               |

| 7   | 0     | 0               | 0        | 0         | 0        | 0                       | 0               | 1                      | 0              | 0               | 1               |

| 8   | 0     | 0               | 0        | 0         | 0        | 0                       | 1               | 0                      | 0              | 0               | 1               |

| 9   | 0     | 0               | 0        | 0         | 0        | 0                       | 0               | 0                      | 0              | 0               | 1               |

| 10  | 1     | 0               | 1        | 1         | 1        | 0                       | 1               | 1                      | 0              | 1               | 1               |

| 11  | 0     | 0               | 0        | 0         | 0        | 0                       | 0               | 1                      | 0              | 0               | 1               |

| 12  | 0     | 1               | 0        | 0         | 0        | 0                       | 1               | 0                      | 0              | 0               | 1               |

| 13  | 0     | 0               | 0        | 0         | 0        | 0                       | 0               | 0                      | 0              | 0               | 1               |

| 14  | 1     | 1               | 1        | 1         | 1        | 0                       | 1               | 1                      | 0              | 1               | 1               |

| 15  | 0     | 0               | 0        | 0         | 0        | 0                       | 0               | 1                      | 0              | 0               | 1               |

Rangkaian uji kedua menghasilkan keluaran dengan kondisi normal atau tanpa adanya kesalahan yaitu  $y_0$  serta kondisi jalur *input* A, B2, C2 dan D mengalami gangguan Sa0 dan Sa1 berturut-turut. Hasil tersebut didapatkan melalui Persamaan 3.2 bisa dilihat pada Tabel 3.4.

Tabel 3.4 Tabel Kesalahan Diagnosa Semua Kesalahan Tunggal dari Potongan 2 Rangkaian IC 74157.

|    |   | Ma | sukar | 1  |   |    |    |     |     |     |     |    |    |    | Ni | lai Ke | eluara | ın  |     |     |     |     |     |     |     |     |     |

|----|---|----|-------|----|---|----|----|-----|-----|-----|-----|----|----|----|----|--------|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| U  | D | С  | B2    | A2 | У | у  | у  | у   | у   | у   | у   | у  | у  | y  | у  | y      | у      | у   | y   | у   | у   | у   | у   | У   | У   | У   | у   |

|    |   |    |       |    | 0 | 10 | 11 | 120 | 121 | 130 | 131 | 40 | 41 | 50 | 51 | 140    | 141    | 150 | 151 | 160 | 161 | 170 | 171 | 180 | 181 | 190 | 191 |

| 0  | 0 | 0  | 0     | 0  | 0 | 0  | 0  | 0   | 1   | 0   | 0   | 0  | 0  | 0  | 0  | 0      | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   |

| 1  | 0 | 0  | 0     | 1  | 0 | 0  | 0  | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0      | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   |

| 2  | 0 | 0  | 1     | 0  | 0 | 0  | 1  | 0   | 1   | 0   | 0   | 0  | 0  | 1  | 0  | 1      | 0      | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   | 0   | 1   |

| 3  | 0 | 0  | 1     | 1  | 0 | 0  | 0  | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0      | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   |

| 4  | 0 | 1  | 0     | 0  | 1 | 1  | 0  | 0   | 1   | 1   | 1   | 1  | 0  | 0  | 1  | 0      | 1      | 0   | 1   | 0   | 1   | 1   | 1   | 0   | 1   | 1   | 1   |

| 5  | 0 | 1  | 0     | 1  | 0 | 0  | 0  | 0   | 0   | 0   | 0   | 1  | 0  | 0  | 0  | 0      | 0      | 0   | 1   | 0   | 1   | 0   | 0   | 0   | 1   | 0   | 1   |

| 6  | 0 | 1  | 1     | 0  | 1 | 1  | 1  | 0   | 1   | 1   | 1   | 1  | 0  | 1  | 1  | 1      | 1      | 0   | 1   | 0   | 1   | 1   | 1   | 0   | 1   | 1   | 1   |

| 7  | 0 | 1  | 1     | 1  | 0 | 0  | 0  | 0   | 0   | 0   | 0   | 1  | 0  | 0  | 0  | 0      | 0      | 0   | 1   | 0   | 1   | 0   | 0   | 0   | 1   | 0   | 1   |

| 8  | 1 | 0  | 0     | 0  | 0 | 0  | 0  | 0   | 0   | 0   | 1   | 0  | 0  | 0  | 0  | 0      | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   |

| 9  | 1 | 0  | 0     | 1  | 0 | 0  | 0  | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0      | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   |

| 10 | 1 | 0  | 1     | 0  | 1 | 0  | 1  | 1   | 1   | 0   | 1   | 1  | 0  | 1  | 0  | 1      | 0      | 0   | 1   | 0   | 1   | 0   | 1   | 1   | 1   | 0   | 1   |

| 11 | 1 | 0  | 1     | 1  | 0 | 0  | 0  | 0   | 0   | 0   | 0   | 1  | 0  | 0  | 0  | 0      | 0      | 0   | 1   | 0   | 1   | 0   | 0   | 0   | 1   | 0   | 1   |

| 12 | 1 | 1  | 0     | 0  | 0 | 1  | 0  | 0   | 0   | 0   | 1   | 0  | 0  | 0  | 1  | 0      | 1      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   |

| 13 | 1 | 1  | 0     | 1  | 0 | 0  | 0  | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0      | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   |

| 14 | 1 | 1  | 1     | 0  | 1 | 1  | 1  | 1   | 1   | 0   | 1   | 1  | 0  | 1  | 1  | 1      | 1      | 0   | 1   | 0   | 1   | 0   | 1   | 1   | 1   | 0   | 1   |

| 15 | 1 | 1  | 1     | 1  | 0 | 0  | 0  | 0   | 0   | 0   | 0   | 1  | 0  | 0  | 0  | 0      | 0      | 0   | 1   | 0   | 1   | 0   | 0   | 0   | 1   | 0   | 1   |

Keterangan : U adalah Pengujian,  $y_{x0}$  adalah Sa0 pada jalur x dan  $y_{x1}$  adalah Sa1 pada jalur x

Berdasarkan Tabel 3.4 didapatkan 10 kelompok kesalahan tunggal yaitu  $\{y_{10}, y_{51}, y_{141}\}$  dikelompokan sebagai  $f_{11}$ ,  $\{y_{11}, y_{50}, y_{140}\}$  dikelompokan sebagai  $f_{12}$ ,  $\{y_{120}, y_{180}\}$  dikelompokan sebagai  $f_{13}$ ,  $\{y_{121}\}$  sebagai kelompok  $f_{14}$ ,  $\{y_{130}, y_{140}, y_{180}\}$  menjadi kelompok  $f_{15}$ ,  $\{y_{131}\}$  sebagai  $f_{16}$ ,  $\{y_{40}, y_{151}, y_{161}\}$  sebagai kelompok  $f_{17}$ ,  $\{y_{41}, y_{150}, y_{160}\}$  menjadi kelompok  $f_{18}$ ,  $\{y_{171}\}$  menjadi  $f_{19}$  dan  $\{y_{181}, y_{191}\}$  menjadi kelompok  $f_{20}$ .

Tabel 3.5 Pengelompokkan Kesalahan Pada Rangkaian Uji 2

|      | $f_0$ | $f_{11}$                | F <sub>12</sub>         | f <sub>13</sub> | $f_{14}$  | f <sub>15</sub>         | f <sub>16</sub>  | f <sub>17</sub>         | f <sub>18</sub>  | f <sub>19</sub>  | F <sub>20</sub>         |

|------|-------|-------------------------|-------------------------|-----------------|-----------|-------------------------|------------------|-------------------------|------------------|------------------|-------------------------|

| Uji  | $y_0$ | $y_{10}$                | $y_{11}$                | $y_{120}$       | $y_{121}$ | y <sub>130</sub>        | y <sub>131</sub> | $y_{40}$                | $y_{41}$         | y <sub>171</sub> | y <sub>181</sub>        |

| - 3- |       | $y_{51}$                | $y_{50}$                | $y_{180}$       |           | $y_{170}$               |                  | $y_{151}$               | $y_{150}$        |                  | <i>y</i> <sub>191</sub> |

|      |       | <i>y</i> <sub>141</sub> | <i>y</i> <sub>140</sub> | _               |           | <i>y</i> <sub>190</sub> | _                | <i>y</i> <sub>161</sub> | y <sub>160</sub> | _                |                         |

| 0    | 0     | 0                       | 0                       | 0               | 1         | 0                       | 0                | 0                       | 0                | 0                | 1                       |

| 1    | 0     | 0                       | 0                       | 0               | 0         | 0                       | 0                | 0                       | 0                | 0                | 1                       |

| 2    | 0     | 0                       | 1                       | 0               | 1         | 0                       | 0                | 0                       | 0                | 1                | 1                       |

| 3    | 0     | 0                       | 0                       | 0               | 0         | 0                       | 0                | 0                       | 0                | 0                | 1                       |

| 4    | 1     | 1                       | 0                       | 0               | 1         | 1                       | 1                | 1                       | 0                | 1                | 1                       |

| 5    | 0     | 0                       | 0                       | 0               | 0         | 0                       | 0                | 1                       | 0                | 0                | 1                       |

| 6    | 1     | 1                       | 1                       | 0               | 1         | 1                       | 1                | 1                       | 0                | 1                | 1                       |

| 7    | 0     | 0                       | 0                       | 0               | 0         | 0                       | 0                | 1                       | 0                | 0                | 1                       |

| 8    | 0     | 0                       | 0                       | 0               | 0         | 0                       | 1                | 0                       | 0                | 0                | 1                       |

| 9    | 0     | 0                       | 0                       | 0               | 0         | 0                       | 0                | 0                       | 0                | 0                | 1                       |

| 10   | 1     | 0                       | 1                       | 1               | 1         | 0                       | 1                | 1                       | 0                | 1                | 1                       |

| 11   | 0     | 0                       | 0                       | 0               | 0         | 0                       | 0                | 1                       | 0                | 0                | 1                       |

| 12   | 0     | 1                       | 0                       | 0               | 0         | 0                       | 1                | 0                       | 0                | 0                | 1                       |

| 13   | 0     | 0                       | 0                       | 0               | 0         | 0                       | 0                | 0                       | 0                | 0                | 1                       |